研究課題

小型飛翔体搭載用プラズマ波動観測アナログASICプリアンプ開発

研究組織

| 代表者 | 尾崎光紀 (金沢大学理工研究域) |

|---|---|

| 共同研究者 | 小嶋浩嗣 (京都大学生存圏研究所) 八木谷聡 (金沢大学理工研究域) |

研究概要

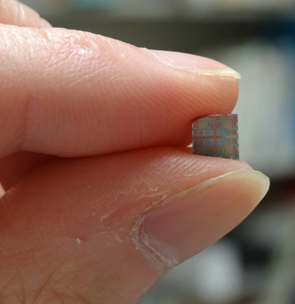

磁気圏のプラズマ波動観測において飛翔体による多点観測が主流である現在、観測性能を劣化させることなく超小型かつ超低消費電力で同じ特性を有するデバイス開発が求められている。特にアナログコンポーネントを多数含むプラズマ波動観測装置に対し、我々はこれまでアナログ ASIC(特定用途向けの集積回路)技術を用いて、電気特性を劣化させることなく装置の超小型化の検討を行ってきた。そして、昨年度までに従来ノイズ特性の面から難しいと考えられていたプラズマ波動観測装置の電磁界センサ感度を決定するプリアンプに対し、0.25 µm の CMOS デバイスを用いて ASIC プリアンプ(電圧雑音 20 nV/√Hz at 100 Hz)の開発に成功している(図を参照)。この成果を踏まえ、本研究では次のステップとして ASIC プリアンプの電気特性を劣化させることなく小型飛翔体(小型衛星、ロケットを想定)に搭載できるまでの耐環境性能(特に放射線、温度)の向上を研究目的とする。

本研究ではアナログASICを対象としているため、耐放射線性能としてトータルドーズ効果のみに着目する。飛翔体を用いた観測では、宇宙環境による放射線、地上においても宇宙線による影響があり、半導体素子への放射線の影響は無視できない。このため、トータルドーズ効果に対して民生品のものより十分にゲート酸化膜の薄い CMOS デバイスを用いて、ゲート酸化膜中の結晶欠陥に捕獲される正孔を低減させ、影響の改善を図る。また、ASIC プリアンプの動作温度範囲を拡大させるために、電源電圧や温度の変動に対して安定した一定の基準電圧または基準電流を作り出すバンドギャップ回路の改良を行う。以上より、極端な小型化と超低消費電力を実現できる CMOS デバイスを用いたアナログ ASIC を飛翔体に搭載できるまで耐環境性能を向上させるよう回路の安定化と改良を図る。

図: 開発した超低ノイズアナログASICプリアンプ

ページ先頭へもどる

2014年7月15日作成